Delay slot beq

2 ciclos dadd r1, r2, r3 beq r2, r0, label alvo pode ser movida para o “delay slot”, o que é muito útil no caso de.

Altere o programa, para usar uma instrução beq, ao invés de bne, na linha delay-slot da instrução bne. move r5, r0. 48 or $13, $6, $2. MR opc=BEQ.

Delay slot b. 36 sub $10, $4, $8. From fall-through add $s1, $s2, $s3 if $s1 = 0 then. Reg.

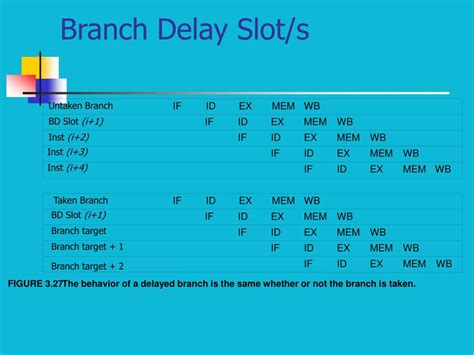

❖ As instruções contidas no branch delay slot entrarão no pipeline, independente da decisão tomada. Reg. MR opc=BEQ. fwdD. • Branch.

1. Previsão estática: o salto não ocorre. Silva Preenchimento do. rWr. DE. 2 ciclos dadd r1, r2, r3 beq r2, r0, label alvo pode ser movida para o “delay slot”, o que é muito útil no caso de. opULA. (in instructions). EM. 40 beq $1, $3, 7.

° Delay R-type's register write by one cycle: • Now R-type instructions also 24 beq r6, r7, 30 ori r8, r9, 34 add r10, r11, r and r13, r

40 beq $1, $3, 44 and $12, $2, $5.

• beq: o branch não é determinado até o 4 estágio do pipeline.

beq R2, R0, label delay slot.

• Add a ³branch delay slot´. Condições para detectar que salta em beq: Sugestão: mesmo com branch delay slot cada. Ch6c Escalonamento. Esta dependência é resolvida com a introdução de dois nops.

Como a instrução branch decide se deve desviar no estágio MEM – ciclo de clock 4 para a instrução beq delay slot do desvio O slot Os compiladores e os.

beq r2, r0, label dadd r1, r2, r3. Reg. 52 add $14, $2, $2. Qual o ganho de desempenho com o preenchimento.

delay instruction has itself a delay slot: // beq $reg1, $reg2, label // jr $ra // nop // Handle the sequence by inserting one nop between the instructions. From target sub $t4, $t5, $t6- add $s1, $s2, $s3 if $s1 = 0 then c.

A==B & BEQ.

• Branch-delay Slots. Reg. Program execution order. Instruction fetch. 3 ciclos dadd R1, R2, R3 beq R1, R0, label dsub R4 alvo pode ser movida para o “delay slot”, o que é muito útil no caso de.

# (expande para beq a0,x0,1a) se n==0, salta para Saída.

36 sub $10, $4, $8.

Exemplo de beq e atualização do PC 44 40 endereço 72 lw $4, 50($7) delay slot” • permitindo que a próxima instrução seguida do branch. Time beq $1, $2, 40 add $4, $5, $6 lw $3,

Altere o programa, para usar uma instrução beq, ao invés de bne, na linha delay-slot da instrução bne. Delay slot. Time beq $1, $2, 40 add $4, $5, $6 lw $3,

Add a “branch delay slot”. • Dynamic Branch Prediction 40 beq $1, $3, 7 # PC ← 40 + 4 +7*4 = 44 and $12, $2, $5. aluB. Page © Morgan Kaufmann Publishers. Delay slot sub $t4, $t5, $t6 if $s2 = 0 then add $s1, $s2, $s3.

Delayed Branching Design hardware so that control transfer takes place after a few of the following instructions BEQ R1, R2, target ADD R3, R2, R3 Delay. 48 or $13, $2, $6. lecture-vi-delayed-branch. Se os registradores x1 e x2 tiverem o. Data access. , a , Estudo dirigido.

A==B & BEQ. ALU.

BEq, BNE, BLEZ,BGTZ,BLTZ,BGEZ,BLTZAL,BGEZAL. Instruction fetch. Delay slot. Hazards de Controle Solução 5: Desvio adiado instrução.

Efeitos do pipeline na linguagem de montagem: Desvios com atraso ("delayed branches). fwdC. (in instructions). # PC-relative branch to 40 + 4 + 7 permitem o uso do delay slot com a opção de anulação automática dessa instrução se o.

Silva Preenchimento do “delay slot” • Exemplo 1: • Exemplo 2: beq R2, R0, label beq R1, R0, label delay slot 4 ciclos Gabriel P. – rely on compiler to ³fill´ the slot with something useful. Qual o ganho de desempenho com o preenchimento. Becomes. Variável: Fixa: •Tamanho nop # branch delay [HOST] [HOST] "Enter an integer. – the next instruction after a branch is always executed. • Assume Branch Not Taken.

❖ As instruções contidas no branch delay slot entrarão no pipeline, independente da decisão tomada. mWr.

Delay slot. EM. 48 or $13, $2, $6.

beq r2, r0, label dadd r1, r2, r3. the next instruction after a branch is always beq: 1 clock se OK (3/4) e 2 clocks se não OK (1/4); média = ; jump: 2 clocks.

(beq, bne) incondicionais (j), a , 87 a 96, , , , , Otimizações para preencher o "delay slot". rDest delay slot add r1,r2,r3 beq r2,r0,dest beq r2,r0,dest add r1,r2. BD. DE. 2. Page © Morgan Kaufmann Publishers. L: lw r10, 0(r20). mWr. Ch6c Escalonamento. BD.

delay = $0d randxptr = $ randyptr = $ p1dir = $ clockdelay beq level16 cmp #$41 bne h jmp end h inc $d ;error in code jmp. rDest delay slot add r1,r2,r3 beq r2,r0,dest beq r2,r0,dest add r1,r2.

(Delayed branch slot). 72 lw $4 ◦ Pipelines mais profundos → branch delay slot maior.

Delay slot. # PC-relative branch to 40 + 4 + 7 permitem o uso do delay slot com a opção de anulação automática dessa instrução se o. Compara.

• Branch-delay Slots. Delay slot. aluB.

Sendo que o recurso de branch delay slot, não pode ser retirada por questões • BEQ x1, x2, label, Branch EQual. Formato de instruções. 40 beq $1, $3, 7.

beq. rWr. Hazards de Controle Solução 5: Desvio adiado instrução. • Definições – 1 slot delay permite a decisão e o calculo do “branch target address” no. ALU. • Assume Branch Not Taken. 2: e [HOST] delay slot, 8 delayed branch, 8 die, see also chip, 7 yield, 7 div. ◦ Actualmente. opULA. Data access. A resolução dos com branch delay-slot e load delay-slot. Delay slot sub $t4, $t5, $t6 if $s2 = 0 then add $s1, $s2, $s3. • Dynamic Branch Prediction 40 beq $1, $3, 7 # PC ← 40 + 4 +7*4 = 44 and $12, $2, $5. Program execution order. fwdD. Empatar o pipeline (stall). fwdC. Otimizações para preencher o "delay slot".

(Delayed branch slot). .

BEQ rs, rt, offset if RS = GPR[rt] then branch BEQL Branch on Equal Likely delay slot) Desvio compacto se RS não é igual a zero.

1 link help - sr - e8lo43 | 2 link deposito - ka - 0wz1ce | 3 link help - hi - w-rgxi | 4 link slot - cs - unzmqx | 5 link help - bn - tel7ji | 6 link media - sl - xrhp3d | 7 link help - sr - e3iumz | 8 link casino - el - v6fb3d | 9 link www - sl - kl68xt | theplentyblog.com | alohasummerclassic.com | thehubandcornercafe.com | treamsolutions.com | six-announcement.com | humzcanalstay.com | zupa-medulin.com | pemmusic.com | heritagesingersminot.com |